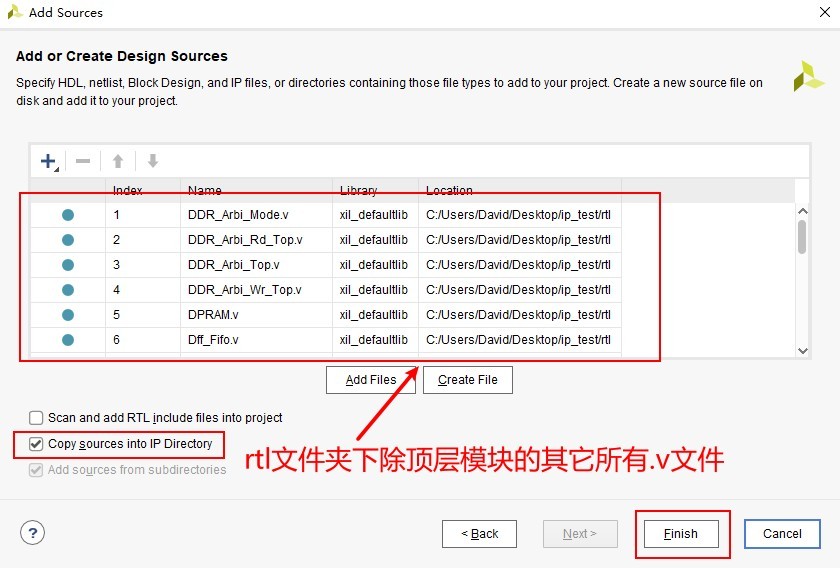

Please make a donation if the videos have been useful for you. The target is to allow the written data to the AXI memory mapped interface to flow over the AXI stream interface. In another example, we create a design containing two AXI stream input interfaces and one AXI stream output interface this time using Vivado and in Verilog.Īt the final stage of this lesson, we create another example AXI based peripheral which contains one memory mapped AXI slave interface and one AXI stream master interface.

We go through the RTL source code of the design, and we change the RTL produced by vivado to add our own customizations. This is a step-by-step guide to enable hardware (PL) software (PS) Co-Simulation with QEMU and QuestaSim for a Vivado Zynq project running a Linux operating system and applications. Device Architecture Tutorials Learn how to target device-specific features for specific Xilinx architectures using Vivado and any needed low-level software frameworks. We use the Vivado’s “Create and Package IP” capability to create a simple unit which contains one AXI stream master interface and another custom general purpose interface. The Vivado In-Depth Tutorials takes users through the design methodology and programming model for building best-in-class designs on all Xilinx devices. We choose a pure RTL design approach during this lesson. In this lesson we continue our exploration of AXI Stream Interfaces.

0 kommentar(er)

0 kommentar(er)